Mitsubishi Addressing

The Mitsubishi driver supports the MELSEC Device style of addressing for retrieving data from the PLC Device registers. Support for serial frames 2C, 3C, and 4C, formats 1, 2, 4 and 5 (only 4C can support format 5) has been added for both the Q series and iQR series PLCs. Support for the 3E and 4E frames has been added for the Q series PLC.

Examples of valid addressing include D0 to read the D device at index 0 in the D register table, or M100 to read the data from index 100 in the Device table. Note that the devices are 0 based.

(For example, D0 or M0).

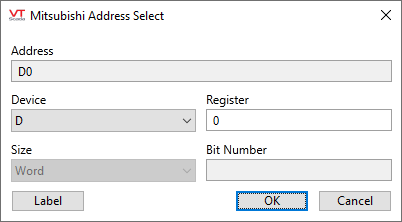

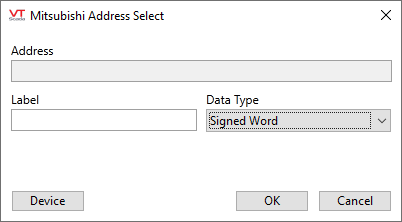

An Address Select dialog is available within your I/O tags when configured to use a Mitsubishi driver. There are two forms:

Form 1: Address Select in Device mode

Form 2: Address Select in Label mode

Device Mode Options - iQR Series

Address

Displays the address resulting from configuration of the following options.

Device

Available device prefixes.

Note that the range available to each is configured within the PLC. Many prefixes are limited to specific data types.

Data Type Prefix Data Type Range D Data register 0-5923327 W Link register 0-5923327

TN Timer value 0-5265151 CN Counter value 0-5265151 STN Retentive timer value 0-5265151 LCN Long counter value 0-2787391 TS Timer contact 0-5265151 TC Timer coil 0-5265151 X Input

0-12287 Y Output 0-12287 M Internal relay 0-94773247 B Link relay 0-5923327 L Latch relay 0-32767 F Annunciator 0-32767 V Edge relay 0-32767 CS Counter contact 0-5265151 CC Counter coil 0-5265151 STS Retentive timer contact 0-5265151 STC Retentive timer coil 0-5265151 LCS Long counter contact 0-2787391 LCN Long counter coil 0-2787391

Register

The index number of the device you wish to read/write.

Size

The data size of the chosen device type.

Bit Number

Used to read a specific bit from a device that contains more than 1 bit and will add the VTScada separator code to the address.

Label Mode Options

The Melsec Label addressing scheme for iQR series PLCs is supported. Use this to define labels, arrays, and structures in the PLC and to use the label names as the address in tags reading from the PLC.

Supported data types include bit, signed word, unsigned word, signed double word, unsigned double word, float, and double precision float. Multidimensional arrays are supported, but no limitation is placed on the index bounds in VTScada. The use of indices greater than those defined in the PLC may work, but is not recommended.

The address used internally by VTScada for Melsec label addressing follows the form of the address from the PLC with the defined data type appended, following a colon. The data type used in the VTScada address must match that defined in the PLC for the given label.

Examples:

MyArray[1,2,3]:bitMyLabel.StructureMember1:UDWordLabel1:Double

Address

Displays the address resulting from configuration of the following options.

Label

Enter the label to be used.

Data Type

Select from the drop-down list of supported data types. The colon separating the data type from the label is added automatic

Support for Q-Series PLCs and Serial Frames

This driver provides support for three CPU types of the Q series PLC, as well as for serial format frames.

Basic CPU

Device

CodeDevice Data type Range SM Specific Relay bit 0-1023 SD

Specific Register word 0-1023 X

Input bit 0-2047 Y

Output bit 0-2047 M

Internal Relay bit 0-8191 L

Latching Relay bit 0-2027 F Alarm bit 0-1023 V

Variant Relay bit 0-1023 B

Link Relay bit 0-2047 D

Data Register word 0-11135 W

Link Register word 0-2047 TS

Timer Contact bit 0-511 TC

Timer Coil bit 0-511 TN

Timer Present Value word 0-511 SS

Retentive Counter Contact bit 0-511 SC

Retentive Counter Coil bit 0-511 SN

Retentive Counter Present Value word 0-511 CS Counter Contact bit 0-511 CC Counter Coil bit 0-511 CN Counter Present Value word 0-511 SB Link Specific Relay bit 0-1023 SW Link Specific Register word 0-1023 S Step Relay bit 0-2027 DX Direct Access Input bit 0-2047 DY Direct Access Output bit 0-2047 Z Variant Register word 0-9 R File Register - Block Toggle Method word 0-32767 ZR File Register - Linked Access Method word 0-65535

High performance CPU

Device

CodeDevice Data type Range SM Specific Relay bit 0-2047 SD

Specific Register word 0-2047 X

Input bit 0-8191 Y

Output bit 0-8191 M

Internal Relay bit 0-8191 L

Latching Relay bit 0-8191 F Alarm bit 0-2047 V

Variant Relay bit 0-2047 B

Link Relay bit 0-8191 D

Data Register word 0-12287 W

Link Register word 0-8191 TS

Timer Contact bit 0-2047 TC

Timer Coil bit 0-2047 TN

Timer Present Value word 0-2047 SS

Retentive Counter Contact bit 0-2047 SC

Retentive Counter Coil bit 0-2047 SN

Retentive Counter Present Value word 0-2047 CS Counter Contact bit 0-1023 CC Counter Coil bit 0-1023 CN Counter Present Value word 0-1023 SB Link Specific Relay bit 0-2047 SW Link Specific Register word 0-2047 S Step Relay bit 0-8191 DX Direct Access Input bit 0-8191 DY Direct Access Output bit 0-8191 Z Variant Register word 0-15 R File Register - Block Toggle Method word 0-32767 ZR File Register - Linked Access Method word 0-1042431

Universal CPU

Device

CodeDevice Data type Range SM Specific Relay bit 0-2047 SD

Specific Register word 0-2047 X

Input bit 0-8191 Y

Output bit 0-8191 M

Internal Relay bit 0-8191 L

Latching Relay bit 0-8191 F Alarm bit 0-2047 V

Variant Relay bit 0-2047 B

Link Relay bit 0-8191 D

Data Register word 0-12287 W

Link Register word 0-8191 TS

Timer Contact bit 0-2047 TC

Timer Coil bit 0-2047 TN

Timer Present Value word 0-2047 SS

Retentive Counter Contact bit 0-2047 SC

Retentive Counter Coil bit 0-2047 SN

Retentive Counter Present Value word 0-2047 CS Counter Contact bit 0-1023 CC Counter Coil bit 0-1023 CN Counter Present Value word 0-1023 SB Link Specific Relay bit 0-2047 SW Link Specific Register word 0-2047 S Step Relay bit 0-8191 DX Direct Access Input bit 0-8191 DY Direct Access Output bit 0-8191 Z Variant Register word 0-15 R File Register - Block Toggle Method word 0-32767 ZR File Register - Linked Access Method word 0-1042431